I’m working on a research project for QUT at the moment at their ARCAA facility, trying to move the brain out of a CPU and onto an onboard FPGA. The end goal of the project is to have a self contained system on a UAV (unmanned aerial vehicle) that is capable of path planning, object detection and avoidance via image processing and radio control to provide status feedback.

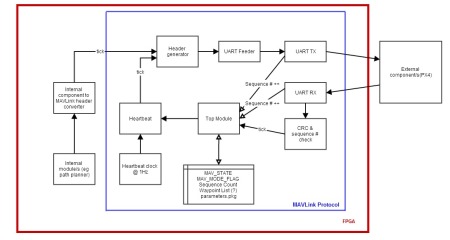

I’m going to be mounting a MicroZED FPGA (control system) onto an AR-Drone 2.0 (quad-copter UAV) which interfaces with a PX4 (flight computer) through a serial UART connection under the MAVLink protocol. Eventually the FPGA will be able to interface with any external component via the UART connection.

One of the biggest problems that I’m facing is the interface between existing technology and the FPGA as all the libraries I’ve come across are written in high level languages like C or Python, rather than HDL (hardware description language) like Verilog or VHDL.

Because of this I’ve decided to translate the entire MAVLink C library into VHDL. Being no small task, it’s taking quite some time and I’m focusing on trying to implement simple modules, such as a status heartbeat, initially and then expanding it until I deem it extensive enough. A flow chart of the basic module structure can be seem below.